| RFC-0030:FIDL 是小端序 | |

|---|---|

| 狀態 | 已接受 |

| 區域 |

|

| 說明 | 宣告 FIDL 為 little endian。 |

| 作者 | |

| 提交日期 (年-月-日) | 2019-01-30 |

| 審查日期 (年-月-日) | 2019-01-30 |

摘要

宣告 FIDL 為 little endian。

提振精神

指定可攜式位元組順序,讓 FIDL 更接近可保存的格式。

初始設計特別選擇主機記憶體順序 (和表示法),避免在傳輸期間需要交換記憶體。這是將 FIDL 訊息安全地表示為 C 結構體的關鍵。不過,我們認為近期內在大端序電腦上執行 Fuchsia 的可能性不大,因此將 FIDL 設為小端序是實用的決定。

設計

目前 FIDL 說明文件指出使用主機位元組順序,但所有現存主機都是小端序。為了朝向可序列化的 FIDL 子集邁進,我們建議目前先宣告 FIDL 為小端序 (這相當於清理文件)。

如果我們需要支援大端平台,許多其他程式碼和文件也需要更新,因此建議屆時再處理 FIDL 的任何變更。

導入策略

準備 CL 來變更 FIDL 說明文件。

在程式碼中,以斷言的形式擷取繫結僅用於小端序機器上的期望。

人體工學

人體工學設計不變。

說明文件和範例

僅變更規格。

回溯相容性

目前沒有變更。 在潛在的未來大端裝置上,FIDL 會受到限制,因此需要進行一些交換 (至少是針對持續性資料結構)。

效能

目前的成效不會受到影響。如果我們支援大端序平台,可能需要 FIDL 修訂版本。

安全性

安全性維持不變。

測試

測試沒有任何異動。

缺點、替代方案和未知事項

有兩種主要替代方案:

- 不提供可序列化功能,但這會限制 FIDL 在某些用途的適用性。

- 提供個別的可保存格式,但這會導致次要序列化路徑需要處處支援。

附加條款

雖然將 FIDL 修正為小端序的技術決策並無爭議,但如同許多事情一樣,這項決策引發了漫長的執行緒。在本課程中,我們學到:

MIPS 過去會根據您在處理器重設後輸入的初始化向量,執行 BE 和 LE (很久以前 MIPS 還是主流時,您可以購買獨立的 MIPS CPU)。部分產品甚至會在重新啟動時切換位元組順序 (別問為什麼)。

雖然 MIPS 已不常見,但我們預期閘極會嵌入 SoC,且位元組順序可能已固定 (且可能固定為小端)。

所有 ARM 核心都會實作大小端。

arm64 可以在 SCTLR 中為每個 EL 選取此選項。 您可以在例外狀況層級轉換時切換位元組順序模式。

arm(32) selects via the SETEND instruction. 執行階段期間,它可以隨時切換位元組順序。 您的編譯器不太可能支援這項功能,但對於某些手動編碼的組件而言,這項功能可能很有用。

IEEE 802.11 是小端序:802.11 流量的管理和控制層會在欄位中使用小端序。所有封裝的通訊協定仍為大端序,802.11 堆疊幾乎不會觸及。

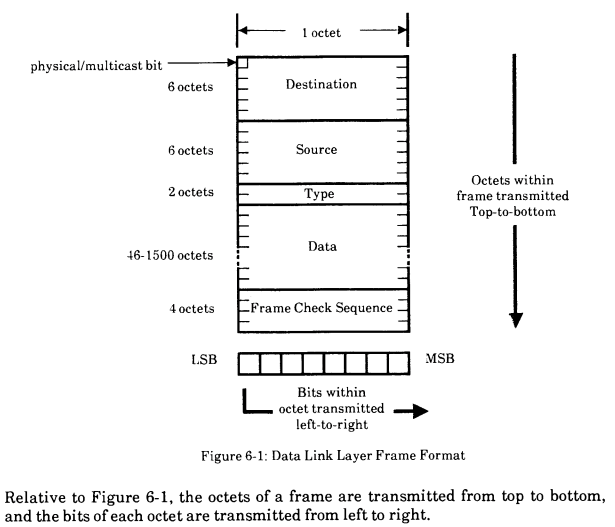

歷史可追溯至 1982 年,當時 Xerox 發明瞭乙太網路。 WLAN 大多會沿用這項決策。 選擇 Little Endian 的原因?這是任意選擇:

乙太網路本身完全不會解讀八位元內的位元,因為這些位元構成 8 位數的二進位數值。不過,由於統一的慣例有助於避免不同電台類型之間不必要的相容性問題,因此「ETHERNET SPECIFICATION: Data Link Layer」的解讀任意定義為「最左側的位元 (第一個傳輸的位元) 是低位 (2^0) 數字,最右側的位元 (最後一個傳輸的位元) 是高位 (2^7) 數字」。

USB 是小端序。

冷知識:MAC 位址不受位元組順序影響,但如果位址採用大端序,您絕對可以在 IP 轉送常式中節省幾個週期,甚至可能在封包以位元組為單位,透過古老的 ~1 Mbps 連結 (每毫秒 ~128 個位元組) 緩慢傳入時,啟動低延遲的「直通」封包轉送。

趣聞:FAT 檔案系統會對標頭中的大多數項目 (但不是所有項目) 使用小端序。如果以大端序讀取整個 FAT 開機磁區的總和檢查碼為 0x1234,則 FAT 檔案系統可做為 Atari ST 上 m68k 處理器的可開機裝置,這表示目前年份實際上仍為 1985 年。

-

「如果

__BYTE_ORDER__等於__ORDER_PDP_ENDIAN__,則 16 位元字組中的位元組會以小端序方式配置,而 32 位元量的 16 位元子字組則會以大端序方式配置。」